ORDER @ Gravitech

ORDER @ Gravitech

ORDER @ Gravitech

ORDER @ Gravitech

| Overview | Schematics | RPi-DAC-RCA+ | Raspberry-Pi | RPi-DAC-Dual | RPi-DAC-SPS | RPi-DAC-SPDIF | Home | RPi-DAC-IF | Order |

|---|---|---|---|---|---|---|---|---|---|

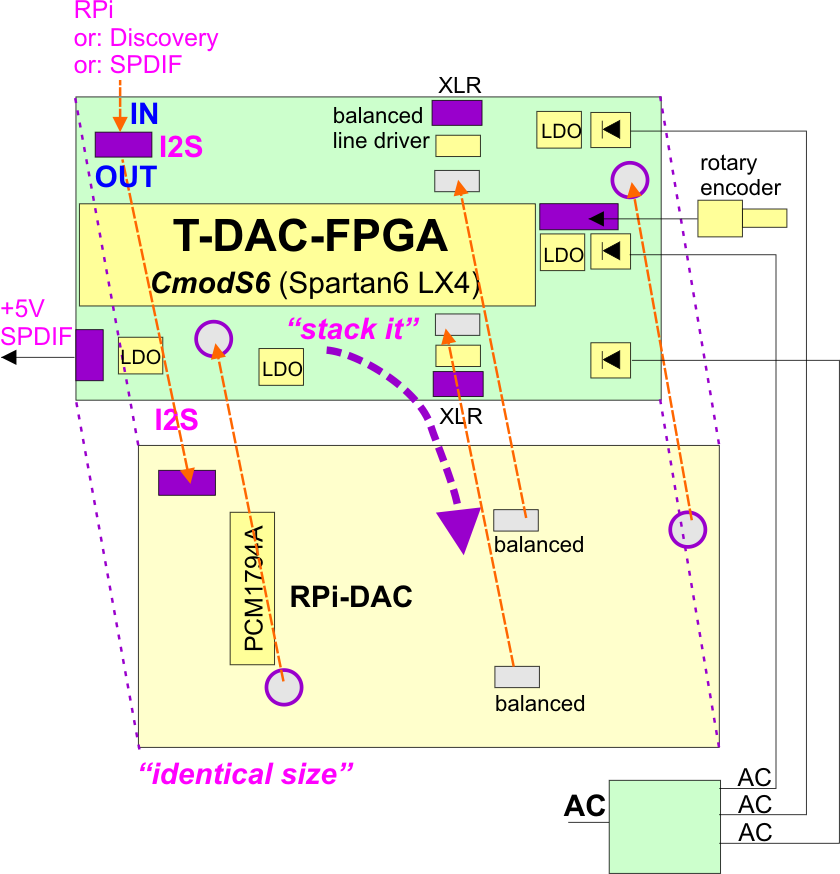

FPGA I2S Filter Module

|

|||||||||

Block Diagram

|

|||||||||

OverviewThis module is optional. It takes (any) I2S input (on top side of PCB), can process and generates a new I2S output (on bottom side of PCB). It can be used in order to do:

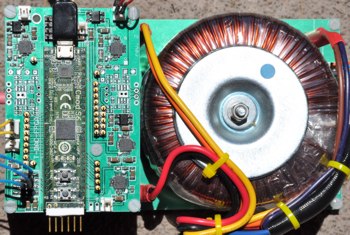

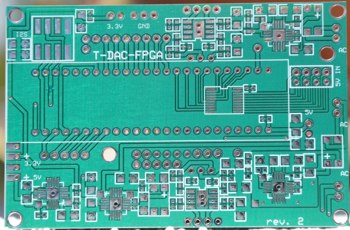

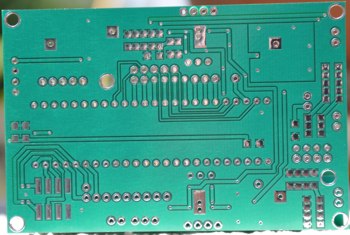

This modules provides also full balanced line drivers so that the balanced DAC output can be connected to XLR connectors. It has onboard LDOs and full-bridge rectifiers with caps so that this module can be fed directly from an AC transformer. The +5V rail is provided also on a header so that an additional module, e.g. RPi-DAC-SPDIF, can be powered directly (stackable). But not enough power to feed the Raspberry Pi from it (FPGA occupies most of the power). This module could be used as standalone extension, e.g. for I2S Out on Raspberry Pi and generate a new I2S signal, e.g. to feed the HiFiBerry. It fits perfect with the RPi and could act as mezzanine board beneath the RPi. It has I2S on top of PCB and I2S Out on the bottom (behaving like an I2S pass-through). The +3.3V is also available on a header (for other extensions) but FPGA might consume most of the power already. A +5V Rotary Encoder can be connected (as inputs) via a level shifter (8 TTL inputs on FPGA, 2 used). All unused FPGA pins are provided at header pins. The three AC inputs can be connected directly with the AC inputs of the RPi-DAC (no wiring needed). The FPGA uses a FIFO and a DCM clock generator so that the output signal is regenerated and potential jitter is eleminated.

Remark: The CmodS6 Spartan6 LX4 FPGA (used as a commercially available module) [1] is quite small (600 slices). Sophisticated upsampling and filtering cannot be done. I am working on a new FPGA module with much higher capacity. The Xilinx ISE project below supports a simple upsampling (rate conversion) from 48KHz to 96KHz, simple stereo wide effect and simple Rotary Encododer volume control (as binary shift operation, not using Dithering). BTW: the FPGA can be used also in order to act as a pre-filter and the DAC is configured for external filtering. So, the DAC can be used as a NOS DAC (only in combination with Dual-Mono because this mode turns the DAC into mono mode). |

|||||||||

FPGA RTL (Xilinx ISE project)CmodS6.zip (1.04MB) Xilinx ISE project Schematicscoming soon Assemblingcoming soon Bill Of Materials (BOM)coming soon |

|||||||||

Design files and docsUltraDAC_RPi_CmodS6.zip (51K) ExpressPCB file (ZIP) |

|||||||||

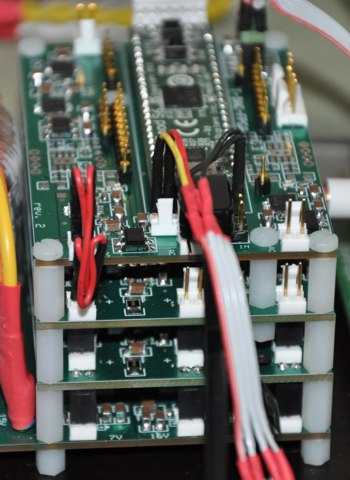

Pictures |

|||||||||

|

|||||||||

References |

|||||||||

|

[1] Digilent CmodS6 [2] see detailed circuit datasheets of original manufacturers |

|||||||||